- English

- Español

- Português

- русский

- Français

- 日本語

- Deutsch

- tiếng Việt

- Italiano

- Nederlands

- ภาษาไทย

- Polski

- 한국어

- Svenska

- magyar

- Malay

- বাংলা ভাষার

- Dansk

- Suomi

- हिन्दी

- Pilipino

- Türkçe

- Gaeilge

- العربية

- Indonesia

- Norsk

- تمل

- český

- ελληνικά

- український

- Javanese

- فارسی

- தமிழ்

- తెలుగు

- नेपाली

- Burmese

- български

- ລາວ

- Latine

- Қазақша

- Euskal

- Azərbaycan

- Slovenský jazyk

- Македонски

- Lietuvos

- Eesti Keel

- Română

- Slovenski

- मराठी

- Srpski језик

Camadas Epitaxiais: A Fundação de Dispositivos Semicondutores Avançados

Figura 1: Ilustra a correlação entre concentrações de dopagem, espessura da camada e tensão de ruptura para dispositivos unipolares.

A preparação de camadas epitaxiais de SiC abrange principalmente técnicas como crescimento por evaporação, epitaxia em fase líquida (LPE), epitaxia por feixe molecular (MBE) e deposição química de vapor (CVD), sendo o CVD o método predominante para produção em massa nas fábricas.

Tabela 1: Fornece uma visão comparativa dos principais métodos de preparação da camada epitaxial.

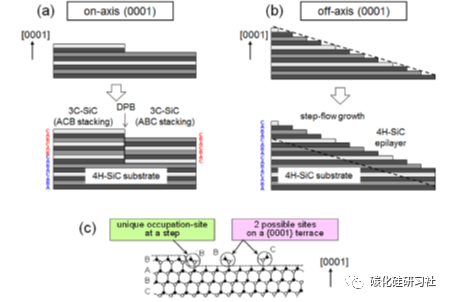

Uma abordagem inovadora envolve o crescimento em substratos fora do eixo {0001} em um ângulo de inclinação específico, conforme representado na Figura 2 (b). Este método aumenta significativamente a densidade do passo enquanto reduz o tamanho do passo, facilitando a nucleação principalmente em locais de agrupamento de etapas e, assim, permitindo que a camada epitaxial replique perfeitamente a sequência de empilhamento do substrato, eliminando a coexistência de politipos.

Figura 2: Demonstra o processo físico de epitaxia controlada por etapas em 4H-SiC.

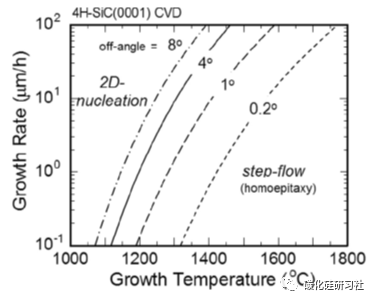

Figura 3: Mostra as condições críticas para o crescimento de DCV em epitaxia controlada por etapas para 4H-SiC.

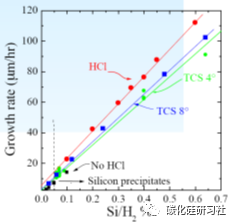

Figura 4: Compara as taxas de crescimento sob diferentes fontes de silício para epitaxia 4H-SiC.

No domínio das aplicações de baixa e média tensão (por exemplo, dispositivos de 1200 V), a tecnologia de epitaxia SiC atingiu um estágio maduro, oferecendo uniformidade relativamente superior em espessura, concentração de dopagem e distribuição de defeitos, atendendo adequadamente aos requisitos para SBD de baixa e média tensão. , MOS, dispositivos JBS e outros.

No entanto, o domínio de alta tensão ainda apresenta desafios significativos. Por exemplo, dispositivos classificados em 10.000 V requerem camadas epitaxiais de aproximadamente 100 μm de espessura, mas essas camadas apresentam espessura e uniformidade de dopagem consideravelmente mais baixas em comparação com suas contrapartes de baixa tensão, sem mencionar o impacto prejudicial de defeitos triangulares no desempenho geral do dispositivo. As aplicações de alta tensão, que tendem a favorecer dispositivos bipolares, também impõem exigências rigorosas à vida útil da portadora minoritária, necessitando de otimização do processo para melhorar este parâmetro.

Atualmente, o mercado é dominado por wafers epitaxiais de SiC de 4 e 6 polegadas, com um aumento gradual na proporção de wafers epitaxiais de SiC de grande diâmetro. O tamanho dos wafers epitaxiais de SiC é fundamentalmente determinado pelas dimensões dos substratos de SiC. Com substratos de SiC de 6 polegadas agora disponíveis comercialmente, a transição da epitaxia de SiC de 4 para 6 polegadas está em constante andamento.

À medida que a tecnologia de fabricação de substratos de SiC avança e as capacidades de produção se expandem, o custo dos substratos de SiC diminui progressivamente. Dado que os substratos representam mais de 50% do custo das pastilhas epitaxiais, espera-se que a diminuição dos preços dos substratos conduza a custos mais baixos para a epitaxia de SiC, prometendo assim um futuro melhor para a indústria.**